Inhaltsverzeichnis

ACHTUNG! Diese Seite wird nicht mehr länger gepflegt. Wechselt auf die englischsprachige Seite für eine aktuelle Anleitung (Link unten links).

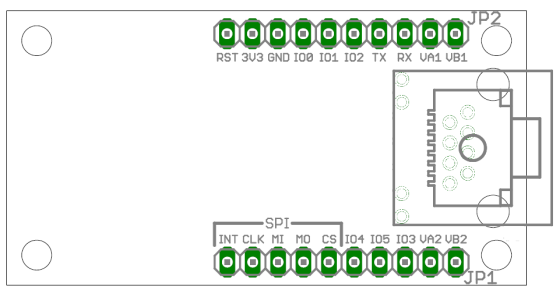

Netzer Pinbelegung

Pins der Pinleiste JP1

| Netzer Name | Beschreibung |

|---|---|

| INT | GPIO-Pins |

| CLK | |

| MI | |

| MO | |

| CS | |

| IO4 | |

| IO5 | |

| IO3 | |

| VA2 | Anschluss für Power-over-Ethernet-Abgriff. Das ist der Mittelabgriff des Ethernetübertragers zwischen den RJ45-Pins 3 und 6. |

| VB2 | Anschluss für Power-over-Ethernet-Abgriff. Dieser Pin wird direkt an der Netzwerkbuchse des Netzers abgegriffen (RJ45-Pins 7 und 8). |

Pins der Pinleiste JP2

| Name | Beschreibung |

|---|---|

| RST | Dieser Pin ist für das Anlegen eines Resetimpulses gedacht. Das Signal ist low-active (d.h. bei einer 0 wird Netzer in den Reset-Zustand versetzt). Das Resetsignal kann außerdem dazu verwendet werden, einen schlafenden Netzer (nach Herunterfahren) wieder aufzuwecken. Der Pin ist optional und kann offen bleiben. |

| 3V3 | Hier wird die Spannungsversorgung angelegt. Die Spannung sollte zwischen 3,1 V und 3,6 V liegen. |

| GND | Massepotential. |

| IO0 | GPIO-Pins |

| IO1 | |

| IO2 | |

| TX | |

| RX | |

| VA1 | Anschluss für Power-over-Ethernet-Abgriff. Das ist der Mittelabgriff des Ethernetübertragers zwischen den RJ45-Pins 1 und 2. |

| VB1 | Anschluss für Power-over-Ethernet-Abgriff. Dieser Pin wird direkt an der Netzwerkbuchse des Netzers abgegriffen (RJ45-Pins 4 und 5). |

Power-over-Ethernet (PoE)

Die vier Anschlüsse VA1, VA2, VB1 und VB2 sind die Abgriffe des Ethernetanschlusses an die ein Power-over-Ethernet-Netzteil angeschlossen werden kann.

Das Bild zeigt den Anschluss am Beispiel des Silver-Telecom-Netzteils Ag9033.

Das Bild zeigt den Anschluss am Beispiel des Silver-Telecom-Netzteils Ag9033.

Übersicht über alle GPIO-Pins

Hier werden nur einige allgemeien Informationen gegeben. Die implementierte Funktionalität der einzelnen Pins hängt vom Projekt ab.

| Netzer Name | ID | Pinleiste | PIC Pin | Strombelastbarkeit Ausgang | Maximale Eingangsspannung | Funktionalität |

|---|---|---|---|---|---|---|

| SPI_INT | j | JP1 | RC2 | 25 mA | 5,5 V | Interruptpin SPI Slave, PWM fähig |

| SPI_CLK | k | JP1 | RC3 | 25 mA | 5,5 V | Takt des SPI- oder I2C-Moduls |

| SPI_MI | l | JP1 | RC4 | 25 mA | 5,5 V | Dateneingang des SPI-Moduls, Datenleitung des I2C-Moduls |

| SPI_MO | m | JP1 | RC5 | 25 mA | 5,5 V | Datenausgang des SPI-Moduls |

| SPI_CS | i | JP1 | RF7 | 2 mA | 5,5 V | Selecteingang des SPI Slaves |

| RX | h | JP2 | RC7 | 25 mA | 5,5 V | Empfangsleitung UART |

| TX | g | JP2 | RC6 | 25 mA | 5,5 V | Sendeleitung UART |

| IO0 | a | JP2 | RB0 | 25 mA | 5,5 V | Interruptfähiger Eingang |

| IO1 | b | JP2 | RB1 | 25 mA | 5,5 V | Interruptfähiger Eingang |

| IO2 | c | JP2 | RB2 | 25 mA | 5,5 V | Interruptfähiger Eingang |

| IO3 | d | JP1 | RD1 | 8 mA | 5,5 V | PWM fähig |

| IO4 | e | JP1 | RA2 | 2 mA | 3,3 V | ADC fähig |

| IO5 | f | JP1 | RA3 | 2 mA | 3,3 V | ADC fähig |